# 宽电压范围输入电源模块设计

王斯 邢海斌

中国电子科技集团公司第十一研究所，北京，100015；

**摘要：**本文描述了一款宽电压范围输入电源模块的设计思路。该电源模块输入电压范围为7V到90V，可输出1.4A平均电流，电路板大小为36mm×12mm。这款宽电压范围输入电源模块实现全国产化，可应用在军品级光电系统伺服控制电路中，功能稳定，性能可靠。

**关键字：**宽电压范围输入；电压转换

**DOI：**10.69979/3041-0673.25.10.011

## 引言

在伺服控制电路中，驱动电源一般以24V、36V、48V、72V等电压值输入，而控制电路中芯片或模块的输入电压一般为12V、5V、3.3V，这时为保证电路正常运行，需要进行降压处理。为提高效率，设计一款较为通用的电源模块，尽可能的适用于不同的电压需求。而线性电源效率低，一般的DC-DC电压输入倍率仅为2倍或4倍，比如9V到36V、18V到72V，范围较小。本篇文章所设计的电源模块推荐电压输入范围为7V到84V，电压输入倍率高达12倍，极限电压输入范围为7V到90V。

## 1 电压转换芯片的选型

常见的开关电源拓扑结构主要为以下几种：

### (1) Buck (降压) 拓扑

功能：将输入电压降低到低于输入电压的输出电压。

特点：输入电压高于输出电压。效率较高，常用于降压场合。

### (2) Boost (升压) 拓扑

功能：将输入电压升高到高于输入电压的输出电压。

特点：输入电压低于输出电压。适用于需要升压的场合。

### (3) Buck-Boost (升降压) 拓扑

功能：既可以降压也可以升压，输出电压可以高于或低于输入电压。

特点：输出电压极性相反。适用于输入电压波动较大的场合。

另外还有Flyback (反激) 拓扑、Forward (正激)

拓扑、Push-Pull (推挽) 拓扑等拓扑结构。根据实际应用需求，选择Buck (降压) 拓扑结构进行宽电压范围输入电源模块设计。

经调研，选择电源芯片型号为SFZ8821M0，生产厂家为中国电子科技集团公司第四十三研究所。该芯片是一款高效率同步整流降压电源芯片，输入电压范围7V到90V，可输出1.4A平均电流。有完善的保护功能，包括峰值电流保护、短路保护和热保护，保证了工作的可靠性。

该芯片的质量等级为军品级，温度范围-55°C~125°C，封装类型为SOE8。

SFZ8821M0的主要功能：

7V to 90V输入电压范围

极低的导通阻抗：500/240mohm

输出电流：1.4A平均电流

具有快速动态响应

频率可调

外置使能控制

峰值电流保护

短路保护

热保护，可自恢复

SFZ8821M0的引脚定义如表1所示。

表1 SFZ8821M0引脚定义

Table 1. Pin Configuration of SFZ8821M0

| 脚位名称 | 脚位编号        | 功能描述                                                                                                                        |

|------|-------------|-----------------------------------------------------------------------------------------------------------------------------|

| NC   | 1           | 无连接                                                                                                                         |

| IN   | 2           | 输入供电脚，和PGND之间至少加4.7uF以上的陶瓷电容                                                                                                |

| EN   | 3           | 外部使能控制，当置高时，芯片工作。切勿悬空                                                                                                       |

| RON  | 4           | 通过与IN间连接的电阻设置内部开关管导通时间。开关频率可以通过下面的公式计算：<br>$f_s(\text{kHz}) = \frac{11 \times V_o(\text{V}) + 500}{R_{ON}(\text{M}\Omega)}$ |

| FB   | 5           | 反馈脚，用于调节输出电压。 $V_{out}(\text{V}) = 1.2(\text{V}) \times (1 + R1/R2)$                                                        |

| VCC  | 6           | 内部LDO输入供电脚                                                                                                                  |

| BS   | 7           | 自举电容脚，通常接100nF陶瓷电容到LX。                                                                                                      |

| LX   | 8           | 开关节点，将电感接到该脚                                                                                                                |

| GND  | Exposed Pad | 内部接地脚，通常会将其和PCB连接，以获得较好的散热性能                                                                                                |

## 2 电路原理图设计

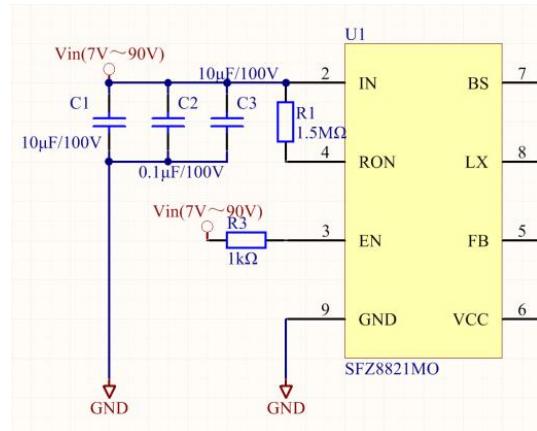

通过查阅 SFZ8821MO 芯片手册, 绘制电路原理图如图 1 和图 2 所示。

图 1 电路原理图 1

Fig. 1. Schematic Diagram of Circuit 1

IN 脚和 GND 之间应至少加 4.7μF 以上的陶瓷电容。选择使用 2 个 10μF/100V 和 1 个 0.1μF/100V 的电容组合<sup>[1]</sup>。

EN 脚为外部使能控制, 当置高时, 芯片工作。连接 1kΩ/0603 电阻使该引脚置高。

选择 1.5MΩ/0603 电阻连接 RON 脚与 IN 脚, 设置内部开关导通时间。开关频率可以通过公式  $F_s(\text{kHz}) = [11 \times V_o(\text{V}) + 500]/R_{on}(\text{M}\Omega)$  计算。

GND 为接地脚。

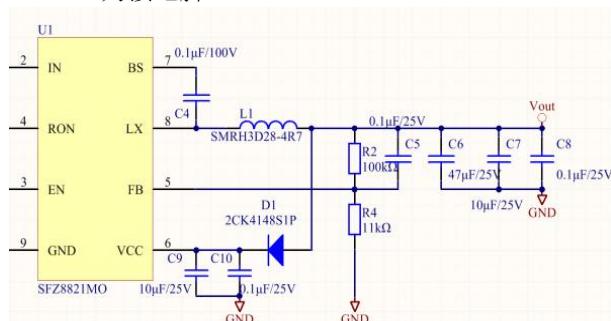

图 2 电路原理图 2

Fig. 2. Schematic Diagram of Circuit 2

FB 为反馈脚, 用于调节输出电压。反馈电阻 R2 和 R4 的值由公式  $V_{out}(\text{V}) = 1.2(\text{V}) \times (1 + R2/R4)$  计算得出。下图为输出电压为 12V、5V、3.3V 时, R2 和 R4 的参考值。

表 2 典型输出电压下反馈电阻的参考值

Table 2. Reference Values of Feedback Resistors at Typical Output Voltages

| $V_{out}$ | R2         | R4          |

|-----------|------------|-------------|

| 12V       | 100kΩ/0805 | 11kΩ/0805   |

| 5V        | 100kΩ/0805 | 31.6kΩ/0805 |

| 3.3V      | 187kΩ/0805 | 107kΩ/0805  |

VCC 脚为内部 LDO 输入供电脚, 连接 10μF/25V 和 0.1μF/25V 的电容组合。并且根据典型电路, 该脚与 LX 脚之间需连接二极管, 选择二极管型号为 BAS21W。

BS 脚为自举电容脚, 接 0.1μF/100V 电容到 LX 脚。

LX 脚为开关节点, 将电感 JSMRH3D28-4R7M 接到该脚。根据芯片手册典型电路, LX 脚与 FB 脚之间连接 0.1 μF/25V 的电容。

电压输出端的滤波电容选择使用 47μF/25V、10μF/25V 和 0.1μF/25V 的电容组合。

电源输入和输出端使用两个单排 4 脚插针。

## 3 PCB 设计

首先, 应先了解 PCB 布局布线的一些基本原则<sup>[2]</sup>:

(1) 布局、布线时应使所有信号回路面积 (特别是高频信号和敏感信号回路面积) 尽可能小。

(2) 对于时钟线、差分线对、复位线及其它高速强辐射或敏感线路, 当线宽为 W 时, 其与相邻线径的中心线距应大于 3W。

(3) 在模拟电路和射频电路设计中, 以及没有电源地平面的双面板中, 常常用保护线来对关键信号进行保护, 使其免受其它信号的串扰。一般保护线连接地网络, 并在线的两端与地相接。频率很高时, 保护线上用多个过孔接地, 过孔之间的距离应小于板上最高频率所对应波长 (λ) 的 1/20。

(4) 高速信号的走线不允许出现锐角和直角。1GHz 以上的信号应该尽量使用圆弧走线。

(5) 为了减少高频信号的辐射和干扰, 高频信号尽量安排在内层。当走线的长度大于信号频率所对应波长 (λ) 的 1/20 时必须走内层。

(6) 任意相邻的信号层应尽可能采取垂直正交的布线方向。

(7) 不要在单板上布设无意义的线; 测试线应尽可能短; 不要在信号层上敷地时形成长条导线。

(8) 信号层上信号线之间的地应通过足够多的过孔接到地平面。

(9) 对于高频信号尤其是高频时钟信号, 连接插座上信号针的四周应用地线插针包围。

(10) 对低速电路、PCB 上信号走向较单一、走线密度较低的情况，地线设计采用梳形电源、地结构（双面板）。

(11) 对较重要的信号加以地保护，布线完成之后将空的地方都敷上地铜皮，用多个过孔将两层的地连接在一起，可以改善回路面积大的问题。

(12) 模拟电路布局时应根据频率高、中、低进行分区，必要时应采取屏蔽隔离措施，以减少电路之间的干扰。

(13) 去耦电容应尽可能靠近V<sub>cc</sub>脚和地之间放置。

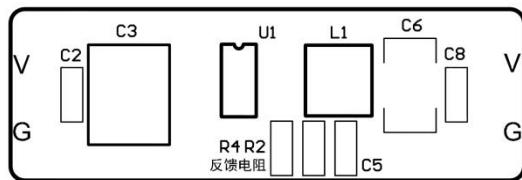

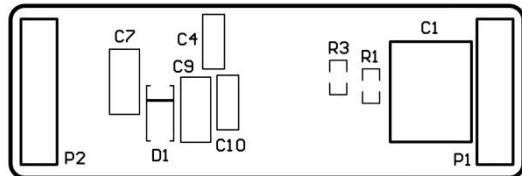

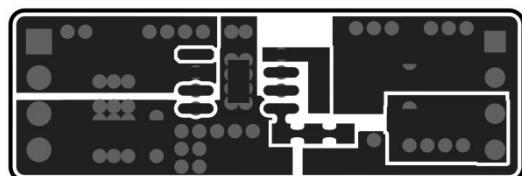

宽电压范围输入电源模块设计为双层板，大小为36mm × 12mm，PCB位置图如图3和图4所示，印制板图如图5和图6所示。

图3 顶层位置图

Fig. 3. Top-layer Layout Diagram

图4 底层位置图

Fig. 4. Bottom-layer Layout Diagram

图5 顶层印制板图

Fig. 5. Top-layer PCB Layout

图6 底层印制板图

Fig. 6. Bottom-layer PCB Layout

按照PCB布局布线的基本原则，在进行宽电压范围输入电源模块PCB布局布线设计中应考虑以下几方面：

(1) 电压输入端滤波电容C1、C2和C3的布局要尽

量靠近U1(SFZ8821MO)的IN脚，大电容在外侧，小电容靠近电源输入引脚，使之与电源和地之间形成的回路最短，VCC脚同理；

(2) 电压输出端滤波电容C6、C7和C8的布局应将小电容靠近U1(SFZ8821MO)的LX脚；

(3) 电源端走线宽度最好大于50mil以上；

(4) R2和R4(反馈电阻)形成的反馈信号回路不能与电源功率回路交叉；

(5) 信号线与其回路构成的环面积要尽可能小；

(6) 走线如果需要弯曲，建议135°而不是90°。

PCB绘制完成后需进行规则检查，如有警告或违反规则，应修改后重新检查，直到无警告或违反规则。

#### 4 验证与测试情况

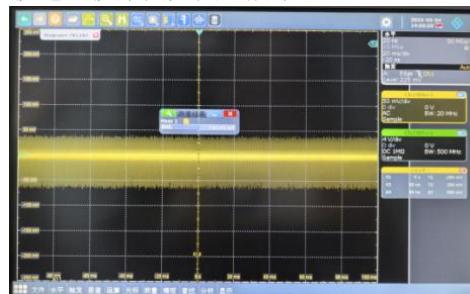

在V<sub>in</sub> = 24V, V<sub>out</sub> = 5V条件下，使用示波器测量输出纹波电压。为了减少高频噪声对纹波电压测量的干扰，同时确保测量结果的准确性，设置BW = 20MHz。经测试，输出纹波电压最大值50mV，RMS值约为7mV。输出纹波电压波形图如图7所示。

图7 输出纹波电压波形图

Fig. 7. Output Ripple Voltage Waveform

根据测试结果可以看出这款宽电压范围输入电源模块输出纹波电压噪声低。并且该电源模块已经在多个光电系统项目中应用，可靠性高，已随系统通过了-40°C~85°C的环境试验。

#### 5 结论

本文所描述的宽电压范围输入电源模块在设计中充分考虑了关于“六性”的设计，具体如下：

(1) 可靠性：电路中对相关器件的选型考虑降额设计<sup>[3]</sup>。

(2) 维修性和测试性：关键器件位于电路板正面，易于测试、诊断故障和维修。

(3) 保障性：所有器件均为国产器件。

(4) 安全性：电路板边缘进行倒角设计。

(5) 环境适应性：所有器件质量等级为军品级。

这款宽电压范围输入电源模块可满足输入电压范围为 7V 到 90V、输出 1.4A 平均电流的需求，并且实现全国产化，可应用在军品级光电系统伺服控制电路中，体积小巧、功能稳定、性能可靠。

### 参考文献

- [1] Qiu Guanyuan, Luo Xianjue. Circuit Theory [M]. Beijing: Higher Education Press, 2006.

邱关源, 罗先觉. 电路 [M]. 北京: 高等教育出版社, 2006.

- [2] Gu Haizhou, Ma Shuangwu. PCB Electromagnetic Compatibility Technology: Design Practices

[M]. Beijing: Tsinghua University Press, 2004.

顾海洲, 马双武. PCB 电磁兼容技术: 设计实践 [M]. 北京: 清华大学出版社, 2004.

[3] GJB/Z 35-93 Derating Design Criteria for Electronic Components [S]. Beijing: Commission of Science, Technology and Industry for National Defense, 1993. GJB/Z 35-93 元器件降额准则 [S]. 北京: 国防科学技术工业委员会, 1993.

作者简介: 王斯(1993-), 女, 汉, 北京, 学士, 硬件设计师, 工程师, 伺服控制器硬件设计, 中国电子科技集团公司第十一研究所。