# 全 CMOS 逻辑 1:4 分接器

程理丽 白天

中国电子科学研究院，北京市，100041；

**摘要：**为了响应数字系统中对高速分接器低功耗与高性能的迫切需求，本文提出并设计了一款全 CMOS 逻辑 1:4 分接器。该设计充分利用了 CMOS 工艺的固有优势，构建了一个由输入缓冲放大器、中间驱动级、施密特触发器以及输出级组成的树型结构系统。CMOS 逻辑电路的技术方案，不仅有效降低了功耗和芯片面积，还实现了轨到轨电平的输出，从而显著增强了噪声裕度。此外，该设计在系统集成时能够与后续电路无缝对接，进一步提升了整体系统的兼容性和性能。本研究旨在为高速分接器的低功耗设计提供一种可行且高效的解决方案。

**关键词：**CMOS 集成电路；分接器；施密特触发器

**DOI：**10.69979/3041-0673.25.06.099

## 引言

随着信息时代的飞速发展，数字信号处理技术日新月异，其中信号的传输速率和频率不断攀升，对信号完整性(Signal Integrity, SI)提出了前所未有的挑战。在高频信号，信号上升和下降的时间急剧缩短，导致信号在传输过程中极易受到延迟、反射、线间串扰、时序错位和振荡等问题的困扰，使数据传输的精确性和系统整体性能受到严重影响。信号完整性问题的严重性日益突出，成为制约芯片功能和性能发挥的关键因素。因此，保证信号的完整性对于保持高速数据传输系统的高性能和稳定性至关重要。

现代社会，信息交换量的激增推动通信技术的迅猛发展，使之成为信息高速公路的中流砥柱。在此背景下，分接器作为数字逻辑系统的核心模块，发挥着将高速串行信号转化为多路低速并行信号的关键作用，对提升通信系统的传输效率和数据处理能力起着举足轻重的作用。

近年来，随着半导体工艺的不断进步，电源电压的逐渐降低，在电路设计领域降低功耗已经成为一个明确而迫切的目标。同时，半导体材料的特征频率  $FT$  不断提高，使得电路的工作速率得到显著提升。在这样的背景下，基于 CMOS 工艺实现的高速甚至超高速缓存器不断的涌现。然而，尽管部分电路设计引入了 CMOS 逻辑电路，但其工作速率通常受限于  $FT$  的 20 倍以下，这主要是因为设计者普遍认为 CMOS 逻辑电路在高速率下的性能受限。因此，如何在保证信号完整性的同时，实现速率提升和功耗降低的双重优化，成为目前分接器技术研究的热点和难点。

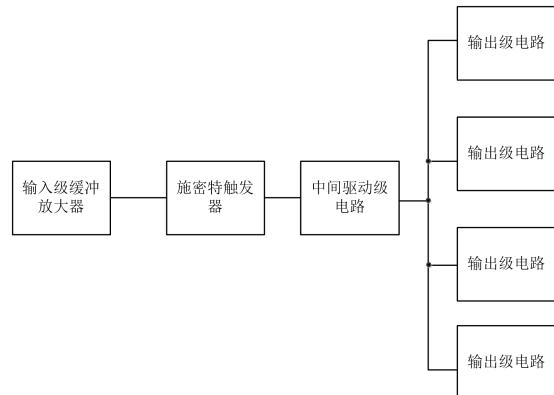

针对以上问题，本文提出了一款创新性的分接器系

统设计，如图 1 所示。该系统由输入缓冲放大器单元、中间驱动级、施密特触发器等多个关键模块和输出级电路组成，旨在通过优化电路结构和参数配置，在优化功耗的同时，有效提高信号处理速度，保证信号完整性，为高速数据传输系统提供更加稳定高效的信号转换解决方案。

图 1 分接器件系统组成架构

## 2 电路设计

### 2.1 输入级缓冲放大器

两级运算放大器理论上可以比较容易的实现高增益，基于功耗的考虑，采用折叠共源共栅结构可以增加输出阻抗。提高输出阻抗一般可以通过增加输出电阻倍数或者增加输入晶体管长度的方法来实现。但是不断增加晶体管的长度会导致版图尺寸过大等问题，同时会增加寄生电容，从而降低工作频率。因此通过增加放大器输出电阻的数值来增加放大器增益，应用增益增强技术，即增加一个的反馈放大器来实现。

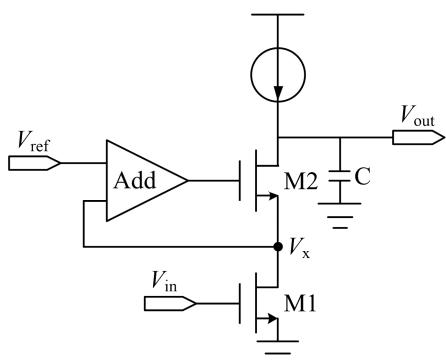

图 2 引入增益增强技术的缓冲放大器

如图 2 所示为增益提升技术。增益增强技术是一种通过负反馈环路增强输出阻抗。当反馈环路稳定时，放大器输入端虚短，负反馈调节  $V_x$  的值等于  $V_{ref}$ 。当输入电流与晶体管尺寸固定，通过该反馈环路决定 M2 的栅极位。当没有 Add 放大器时，在小信号分析中，由辅助定理得电压增益  $A_v = -G_m R_{out}$ ，针对图 2 可以认为  $G_m = g_{m1}$ ，为了计算  $R_{out}$ ，可以把电路简化等效为带负反馈电阻  $r_{o1}$  的共源级，因此得

$$R_{out} = r_{o2} (1 + g_{m2} r_{o1}) \quad (1)$$

所以，共源共栅放大器的增益是：

$$A_v = g_{m1} \cdot r_{o2} (1 + g_{m2} r_{o1}) \quad (2)$$

加入 Add 放大器后，输出电阻就变成了：

$$R_{out} = r_{o2} [1 + (1 + A_{dd}) g_{m2} r_{o1}] \quad (3)$$

则增益变为

$$A_v = g_{m1} \cdot r_{o2} [1 + (1 + A_{dd}) g_{m2} r_{o1}] \quad (4)$$

这说明采用增益增强技术后，输出电阻比原来增加了  $A_{dd}$  倍，增益比原来有所增加。在增益增强技术中，辅助放大器不会降低输出摆幅，对等效输入噪声同样没有造成影响，可广泛应用于大幅度、高速、低噪声放大器架构中。

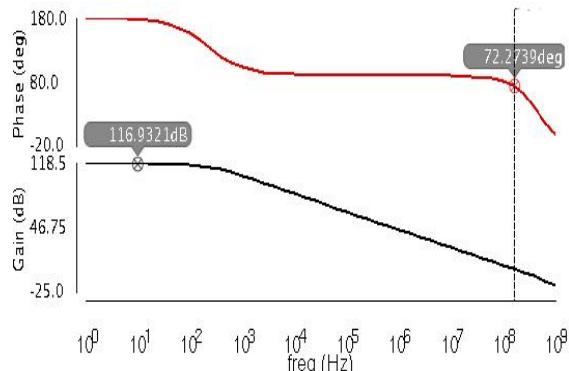

论文设计的运放得到压摆率  $162V/\mu s$ ；最后进行交流模拟，结果如图 3 所示，运放增益为  $116.9dB$ ，相位裕度为  $72$ 。

图 3 输入级缓冲放大器的交流仿真曲线

## 2.2 施密特触发器电路设计

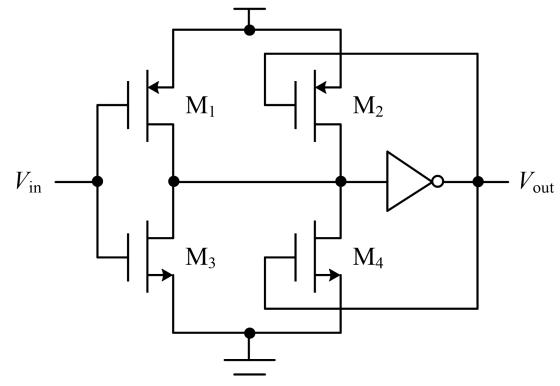

施密特触发器电路主要是对前级信号进行波形整形，以满足系统对信号逻辑电平的要求。由于驱动能力、波形的上升、下降时间、占空比等关键指标的制约，在前级与后级电路之间设计施密特触发器电路。同时加入反相器链增强逐级的驱动能力。为了保证其最短的延时，一个相片链的级数和尺寸需要合理设计。为了提升波形的传输质量，设计如图 4 所示的缓冲器电路。该电路通过阈值电压的设计，滤除掉高频的毛刺与适当的过冲与回落电压，同时降低波形翻转时间。施密特触发器具有不同的逻辑翻转阈值电压，当适当的“噪声”干扰来时，没有超过阈值，逻辑就不会翻转，因此阈值窗口设计代表了系统的噪声容限。

图 4 施密特触发器的拓扑结构

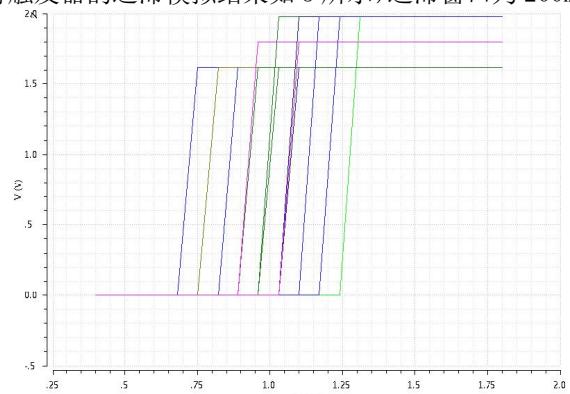

假设输入  $V_{in}$  和  $V_{out}$  最初值为 0。当晶体管 M4 截止，晶体管 M2 导通是通过反馈实现的。当输入信号传递给 M1 的漏极，输出信号的翻转可以加剧 M2 与 M4 棚极电压的变化，从而进一步加速输出信号的变化。当输入信号从 0 跳变到 1，M1 的漏极信号从 1 跳变为 0，输出信号也是 0 跳变到 1，此时 M2 晶体管处于逐渐关闭过程，而 M4 逐渐导通，从而加速 M2 漏极电压的下降，进一步加速输出信号 0 跳变到 1 过程。不同 Corner 施密特触发器的迟滞模拟结果如 5 所示，迟滞窗口为  $200mV$ 。

图 5 在不同 corner 下施密特触发器的迟滞仿真曲线

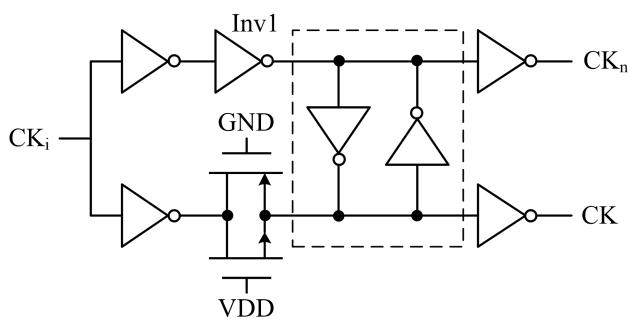

## 2.3 输出级电路设计

时钟缓冲电路设计于 1:4 分接器, 后级采用 2 个 1:2 分接单元, 以达到最后 1:4 分接器的作用。设计如下图所示缓冲器电路, 采用差分结构实现, 避免时钟重叠的问题。设计中调节传输门的传输时延等于反相器 INV 1 的传输时延, 从而得到相位相反、上升下降时间相等交叉对称的时钟信号。在传输路径长采用正反馈放大器对电路, 可以有效提升上升下降时间, 进一步使得时钟信号占空比为 50%。

图 6 时钟缓冲器的拓扑结构

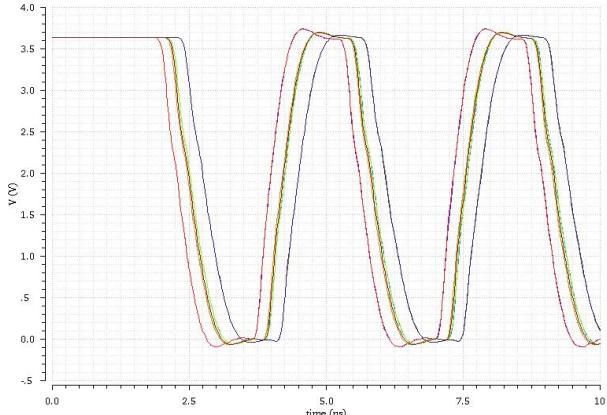

上述全 CMOS 逻辑 1:4 分接器系统的工艺角模拟结果如图 7 所示, 满足 250MHz 频率输出。

图 7 全 CMOS 逻辑 1:4 分接器系统的工艺角仿真曲线

### 3 总结

针对数字系统对高速分接器低功耗、高性能的迫切需求，提出并设计出全 CMOS 逻辑。这一设计充分挖掘了 CMOS 工艺的内在优势，构建了包含输入缓冲放大器、中间驱动级、施密特触发器和输出级的树状结构体系。这一设计不仅显著降低了功耗和芯片面积，通过实现轨电平输出增强了噪声裕度，还保证了与后续电路的无缝对接，增强了系统集成的兼容性和性能，为高速分接器

的低功耗设计提供了可行高效的解决方案。

在电路设计部分，详细阐述了输入缓冲放大器电路的创新设计。通过增益增强技术有效提高了输出阻抗和增益，确保了高精度放大器的使用性能。施密特触发器电路设计通过整形缓冲电路将含有噪声或缓慢变化的输入信号转化为干净的数字信号，从而显著提高了系统的抗干扰能力。输出级电路的设计，既解决了时钟重叠的问题，又保证了信号转换速度和 50% 的占空比，满足了高速传输数据的需求。

通过模拟验证,设计的分接器在增益、压摆率和相位裕度方面表现优异,并且系统在不同的工艺角度下稳定工作于250MHz频率,充分验证该电路的可靠性。该研究为高速差分的驱动电路设计提供了新的设计架构,对于推动高速数据传输系统的性能提升和功耗优化具有非常重要的实践意义和理论价值。今后,我们将不断探索更加先进的工艺技术和电路优化方法,进一步提高分接器的性能和效率,为信息时代的通信技术进步添砖加瓦。

## 参考文献

- [1] Hayong Jung, et al. CMOS High-Voltage Analog 1 - 64 Multiplexer/Demultiplexer for Integrated Ultrasound Guided Breast Needle Biopsy [J]. IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control, 2018, 65(8):1334-1345.

[2] Akira T., et al. A redundant multivalued logic for a 10-Gb/s CMOS demultiplexer IC [J]. IEEE Journal of Solid-State Circuits, 2003, 38(1):107-113.

[3] Akira T., et al. 0.18-/spl mu/m CMOS 10-Gb/s multiplexer/demultiplexer ICs using current mode logic with tolerance to threshold voltage fluctuation [J]. IEEE Journal of Solid-State Circuits, 2001, 36(6):988-996.

[4] Sami U.R., et al. A 48 mW 18 Gb/s Delay-Line Based 1:4 Demultiplexer in 45-nm RFSOI CMOS [C]. 2019 IEEE 15th Conference on Ph.D Research in Microelectronics and Electronics (PRIME), Lausanne, Switzerland, 2019:213-216.

[5] 吴大正等. 信号与线性系统分析 [M]. 第3版. 北京: 高等教育出版社. 2000: 28-33.